Too much dependency on central device has its own drawbacks. There are mainly three types of data hazards.

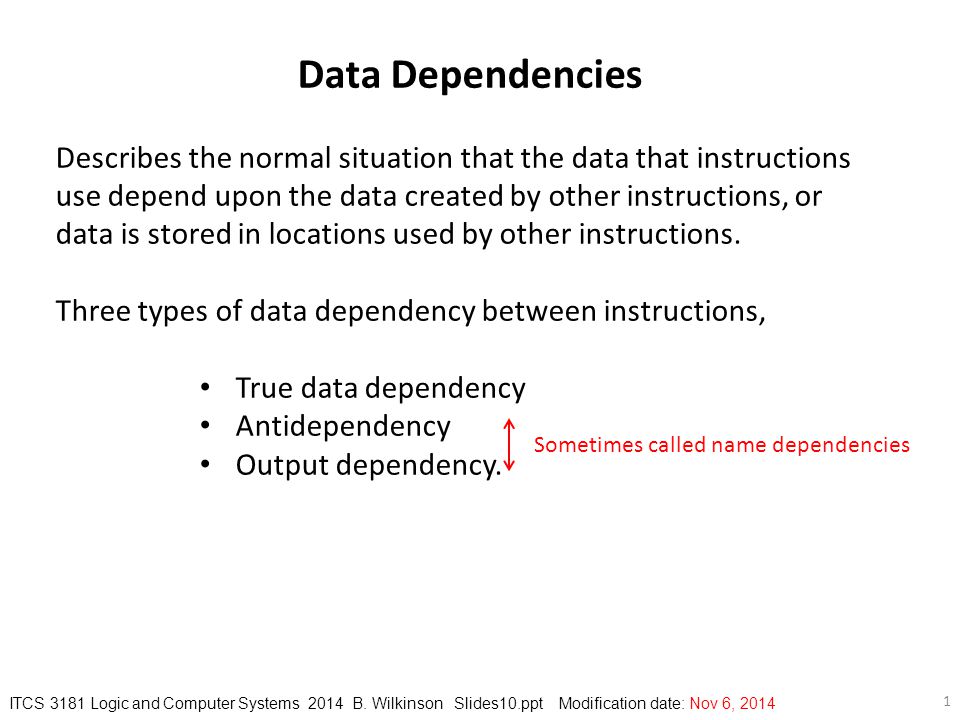

Data Dependencies Describes The Normal Situation That The Data That Instructions Use Depend Upon The Data Created By Other Instructions Or Data Is Stored Ppt Download

Write after read WAR an anti-dependency.

. Reduced Instruction Set Computer RISC Complex Instruction Set Computer CISC Minimal instruction set computers MISC Very long instruction word VLIW Explicitly parallel instruction computing EPIC One instruction set computer OISC Zero instruction set computer ZISC Get an overview of each of the above Instruction Sets. The instruction is divided into 5 subtasks. Data dependencies in straight-line code.

There are two types of data dependence true data dependences and name dependences. A SIMD architecture is one that takes a single instruction at a time but can operate on multiple pieces of data at a time. Instruction i produces a result that may be used by instruction j or Instruction j is data dependent on instruction k and instruction k is data dependent on instruction i.

Contents 1 Data dependencies 11 Flow dependency True dependency 12 Anti-dependency 13 Output dependency 2 Control dependency. An instruction j is data dependent on instruction i if either of the following holds. Pipelining is a technique where multiple instructions are overlapped during execution.

1 answer 95 views. If the hub goes down the whole system is dead. Consider two instructions i1 and i2 with i1 occurring before i2 in program order.

Read after write RAW a true dependency. If it fails the whole network goes down. Read after Write RAW Write after Read WAR Write after Write WAW and Read after Read RAR.

Pipeline is divided into stages and these stages are connected with one another to form a pipe like structure. 1 RAW Read after Write FlowTrue data dependency 2 WAR Write after Read Anti-Data dependency 3 WAW Write after Write Output data dependency Let there be two instructions I and J such that J follow I. Pipelining increases the overall instruction throughput.

Data dependencies for memory data can be interpreted in a similar method. What are types of hazards are mitigated by forwarding and how. Data name and control.

Anti dependence denoted by S1 S2. These are explained as follows below. A data dependency occurs when an instruction needs data that are not yet available.

The potential overlap among instructions is called instruction level parallelism. It can be thought of as a simple parallel computing strategy. Two statement are output dependent if they produce the same output variable.

There are three types of dependencies. It is also known as True dependency or Flow dependency. Instruction-level parallelism ILP is a measure of how many of the operations in a computer program can be performed simultaneously.

Write after write WAW an output dependency. Statement S2 is independent on statement S1 if S2 follows S1 in program order and if output of S2 overlaps the input of S1. In pipelining the instruction is divided into the subtasks.

There are mainly six types of normalization in Database. The dependencies in the pipeline are called Hazards as these cause hazard to the execution. Ii During the process of normalization we can identify dependencies that causing the problems when deleting or updating.

The dependency of the whole topology on one single point the hub. Problem 1 65 a What are Dependency and Hazard in a pipeline processor architecture. There are four types of data dependencies.

Essentially an occurrence of a hazard prevents an instruction in the pipe from being executed in the designated clock cycle. Instruction 2 is truly dependent on instruction 1 as the final value of B depends on the instruction updating A. Although a star requires far less cable than a mesh each node must be linked to a central hub.

Data Dependence - 2 Output dependence denoted by S1 S2. B What are the different types of Hazards. In the above instruction 3 is truly dependent on instruction 2 as the final value of C depends on the instruction updating B.

Read after write RAW. Pipelining improves the throughput of the system. Instructions enter from one end and exit from another end.

Read after Write RAW. CS 6303 - Computer Architecture Unit 4 Q A 1. Follows that 3 is dependent on 1 as well.

In compiler theory the technique used to discover data dependencies among statements or instructions is called dependence analysis. D For the following RISC V instructions identify dependencies and hazards. RAW dependencies Consider two assembly language instructions.

Instruction fetch instruction decode operand fetch instruction. We use the word Dependencies and Hazard interchangeably as these are used so in Computer Architecture. The biggest difference between SIMD and MIMD is that MIMD can perform multiple instructions on multiple pieces of data at a time.

Each subtask performs the dedicated task. Explain instruction level parallelism and its difficulties in implementing it. Read after read RAR is not a hazard case.

Asked Mar 28 in Computer Architecture by anonymous. Pipelining organizes the execution of the multiple instructions simultaneously. I Normalization reduces Data Redundancy it is the unnecessary repetition of a field.

What are the different forwarding methods. Explain each one of the list viewpoints based on computer architecture. A collision occurs when an instruction cannot proceed because previous instructions did not complete certain operations.

Straight-line code can include three different types of dependencies known as RAW Read after Write WAR Write after Read and WAW Write after Write dependencies. A definition of computer architecture is built on four basic viewpoints namely the structure the organization the implementation and the performance.

Source Dependency An Overview Sciencedirect Topics

Control Dependency An Overview Sciencedirect Topics

0 Comments